# BC2502A/BC2502B Sub-1GHz Low-IF FSK RF Receiver

#### **Features**

· Frequency bands

BC2502A: 315MHz, 433MHz

BC2502B: 315MHz, 433MHz, 868MHz, 915MHz

• Operating voltage range: 2.4V~5.5V

• 0.5µA deep sleep current with data retention

· Low RX current

• 4.5mA @ 433MHz

• 5.8mA @ 868MHz

· Supports FSK modulation

• FSK support up to 50Ksps symbol rate

• Good reception sensitivity under 0.1% BER (BW=93.6k)

• -108dBm @ 25Kbps, 433MHz

• Wide RF input power range: from sensitivity to +10dBm

• Support 2-wire I<sup>2</sup>C interface for operation configuration

• On-chip VCO and Fractional-N synthesizer with integrated loop filter

• Supports low cost 16MHz crystal

FCC/ETSI Compliant

• Package type: 10-pin SOP-EP

## **Applications**

- · Iron rolling doors

- · Ceiling lamps

- · Wireless switches

- · Drying racks

- · Wireless doorbells

- Integrated ceilings

- Other wireless products

### **General Description**

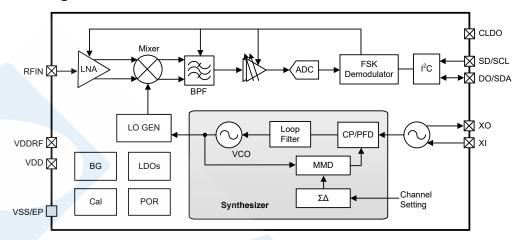

The BC2502x receiver devices adopt a fully-integrated, low-IF FSK receiver with an automatic gain control (AGC) function and a fully-integrated FSK demodulator. The synthesizer is formed by an integrated VCO and a fractional-N PLL to support the 315, 433, 868, and 915MHz frequency bands. The devices only require a crystal and a minimum number of passive components to fully implement a FSK receiver. With this high level of functional integration, these devices provide excellent solutions for low-cost, low power wireless applications.

The devices achieve -112dBm sensitivity for the 433.92MHz bands. They operate from a supply voltage of 2.4V to 5.5V and typically require 4.5mA at 433.92MHz. The devices support a sniff RX mode, where the on/off RX mode function can be controlled by an MCU to achieve a lower than average power consumption using duty RX mode operation.

The BC2502 series offers two types of ICs. One is the BC2502A which covers the 315 and 433MHz bands while the BC2502B offers a choice of four frequency bands.

#### Selection Table

| Part Number | Frequency Band                 |

|-------------|--------------------------------|

| BC2502A     | 315MHz, 433MHz                 |

| BC2502B     | 315MHz, 433MHz, 868MHz, 915MHz |

Singel 3 | B-2550 Kontich | Belgium | Tel. +32 (0)3 458 30 33 info@alcom.be | www.alcom.be Rivium 1e straat 52 | 2909 LE Capelle aan den IJssel | The Netherlands Tel. +31 (0)10 288 25 00 | info@alcom.nl | www.alcom.nl

Rev. 1.00 1 January 12, 2022

## **Block Diagram**

# **Pin Assignment**

## **Pin Description**

| Pin No. | Pin Name              | I/O   | Description                                                |  |  |  |

|---------|-----------------------|-------|------------------------------------------------------------|--|--|--|

| 1       | SD/SCL <sup>(1)</sup> | DI    | RX mode shut-down control, should be pulled low in RX Mode |  |  |  |

| '       | SD/SCL**              | DI    | I <sup>2</sup> C clock input line in Configuration Mode    |  |  |  |

| 2       | NC                    | _     | Not connected                                              |  |  |  |

| 3       | RFIN                  | Al    | RF LNA input                                               |  |  |  |

| 4       | AVDD                  | PWR   | Analog power supply                                        |  |  |  |

| 5       | XO                    | AO    | Crystal oscillator output                                  |  |  |  |

| 6       | XI                    | Al    | Crystal oscillator input                                   |  |  |  |

| 7       | DVDD                  | PWR   | Digital power supply                                       |  |  |  |

| 8       | NC                    | _     | Not connected                                              |  |  |  |

| 9       | CLDO                  | PWR   | LDO output, connected to a bypass capacitor                |  |  |  |

| 10      | DO/SDA <sup>(1)</sup> | DO    | Demodulated data output in RX Mode                         |  |  |  |

| 10      | DO/SDA                | DI/DO | I <sup>2</sup> C data line in Configuration Mode           |  |  |  |

| _       | VSS/EP(2)             | PWR   | Exposed pad, must be connected to ground                   |  |  |  |

Legend: DI: Digital Input;

DO: Digital Output;

AI: Analog Input;

AO: Analog Output;

PWR: Power.

Note: 1. The DO/SDA & SD/SCL pins are default connected to a pull-high resistor after a power on reset. After entering the RX mode, these pull-high resistors are disconnected automatically. An analog debounce function is added to these two pins.

- 2. The VSS/EP pin located at the exposed pad.

- 3.The backside plate of EP shall be well soldered to ground on PCB, otherwise it will downgrade RF performance.

Rev. 1.00 2 January 12, 2022

# **Absolute Maximum Ratings**

| Supply VoltageV <sub>SS</sub> -0.3V to 5.5V                  | Storage Temperature50°C to 125°C  |

|--------------------------------------------------------------|-----------------------------------|

| Input Digital VoltageV <sub>SS</sub> -0.3V to $V_{DD}$ +0.3V | Operating Temperature40°C to 85°C |

| Input Analog VoltageV <sub>SS</sub> -0.3V to 2.1V            | ESD HBM $\pm 2kV$                 |

<sup>\*</sup>Devices being ESD sensitive. HBM (Human Body Mode) is based on MIL-STD-883.

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

## D.C. Characteristics

Ta=25°C, V<sub>DD</sub>=5.0V, f<sub>XTAL</sub>=16MHz, FSK demodulation with matching circuit, unless otherwise specified

| Symbol           | Parameter                            | Conditions | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------|------------|------|------|------|------|

| T <sub>OP</sub>  | Operating Temperature                | _          | -40  | _    | 85   | °C   |

| V <sub>DD</sub>  | Operating Voltage                    |            | 2.4  | 5.0  | 5.5  | V    |

| Current Co       | nsumption                            |            |      |      |      |      |

| I <sub>SLP</sub> | Current Consumption, Deep Sleep Mode | _          | _    | 0.5  | _    | μΑ   |

|                  |                                      | @ 315MHz   | _    | 4.7  | _    |      |

|                  | Current Consumption DV Made          | @ 433MHz   | _    | 4.5  | _    | A    |

| I <sub>RX</sub>  | Current Consumption, RX Mode         | @ 868MHz   | _    | 5.8  | _    | mA   |

|                  |                                      | @ 915MHz   | _    | 5.8  | _    |      |

| R <sub>PH</sub>  | Pull-high Resistance for I/O Ports   | _          | _    | 100  | _    | kΩ   |

## A.C. Characteristics

Ta=25°C, V<sub>DD</sub>=5.0V, f<sub>XTAL</sub>=16MHz, FSK demodulation with matching circuit, unless otherwise specified

| Symbol                           | Parameter                     | Min.                | Тур.     | Max.   | Unit |       |  |

|----------------------------------|-------------------------------|---------------------|----------|--------|------|-------|--|

| Receiver                         | Characteristics               |                     |          |        |      |       |  |

|                                  |                               | BC2502A/BC2502B     | -        | 315    | _    |       |  |

| $f_{RF}$                         | RF Frequency Range            | BC2502A/BC2502B     | _        | 433.92 | _    | MHz   |  |

| IRF                              | RF Frequency Range            | BC2502B only        |          | 868.35 |      | IVITZ |  |

|                                  |                               | BC2502B only        | _        | 915    | _    |       |  |

| SR                               | Symbol Rate                   |                     | 1        | _      | 50   | Ksps  |  |

| f <sub>DEV</sub>                 | Frequency Deviation           | _                   | 4        | _      | 25   | kHz   |  |

|                                  | RX Sensitivity – 315MHz       | SR=1Ksps, BER<0.1%  | _        | -106   | _    |       |  |

|                                  | (Instrument: Keysight E4438C) | SR=10Ksps, BER<0.1% |          | -108   | _    |       |  |

|                                  | RX Sensitivity – 433.92MHz    | SR=1Ksps, BER=0.1%  | _        | -108   | _    |       |  |

| P <sub>SENS</sub> <sup>(1)</sup> | (Instrument: Keysight E4438C) | SR=10Ksps, BER=0.1% | _        | -108   | _    | dBm   |  |

| PSENS''                          | RX Sensitivity – 868.35MHz    | SR=5Ksps, BER=0.1%  | _        | -105   | _    | иын   |  |

|                                  | (Instrument: Keysight E4438C) | SR=10Ksps, BER=0.1% | _        | -105   |      |       |  |

|                                  | RX Sensitivity – 915MHz       | SR=5Ksps, BER=0.1%  | _        | -104   | _    |       |  |

|                                  | (Instrument: Keysight E4438C) | SR=10Ksps, BER=0.1% | _        | -104   | _    |       |  |

| 0.                               | Descine Couries Francisco     | 25MHz~1GHz          | <u> </u> | _      | -57  | dD:   |  |

| SE <sub>RX</sub>                 | Receiver Spurious Emission    | Above 1GHz          | 1GHz —   |        | -47  | dBm   |  |

|                                  | Displains Immunity            | ±2MHz offset        | _        | 40     | _    | dDa   |  |

|                                  | Blocking Immunity             | ±10MHz offset       | _        | 64     |      | dBc   |  |

Rev. 1.00 3 January 12, 2022

| Symbol            | Parameter                             | Conditions      | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------|-----------------|------|------|------|------|

| RXst              | RX Mode Settling Time                 | 49US XO         | _    | 1.5  | _    | ms   |

| <b>RAST</b>       | (Deep Sleep Mode to RX Mode Data Out) | SMD3225 XO      | _    | 2    | _    | ms   |

| LO Chara          | acteristics                           |                 |      |      |      |      |

|                   |                                       | BC2502A/BC2502B | 300  | _    | 360  |      |

| f <sub>LO</sub>   | Frequency Coverage Range              | BC2502A/BC2502B | 390  | _    | 450  | MHz  |

|                   |                                       | BC2502B only    | 850  | _    | 935  |      |

|                   | Frequency Resolution                  | _               | _    | _    | 0.1  | kHz  |

|                   | Synthesizer Locking Time              | _               | _    | 130  | _    | μs   |

| Crystal C         | Scillator Characteristics             |                 |      |      |      |      |

| f <sub>XTAL</sub> | Crystal Frequency                     | General case    | _    | 16   | _    | MHz  |

| 4                 | V'tal Startus Time(2)                 | 49US XO         | _    | 0.5  | _    | ms   |

| t <sub>SU</sub>   | X'tal Startup Time <sup>(2)</sup>     | SMD3225 XO      | _    | 1.5  | _    | ms   |

| ESR               | X'tal Equivalent Series Resistance    | _               | _    | _    | 100  | Ω    |

| CL                | X'tal Load Capacitance                | _               | _    | 16   | _    | pF   |

| TOL               | X'tal Tolerance <sup>(3)</sup>        | _               | -20  | _    | +20  | ppm  |

Note: 1. 315/433MHz Bands Digital Filter BW=93.6kHz 868/915MHz Bands Digital Filter BW=187.2kHz

- 2. The X'tal startup time depends on crystal property.

- 3. This is the total tolerance including (1) Initial tolerance (2) Crystal loading (3) Aging (4) Temperature dependence.

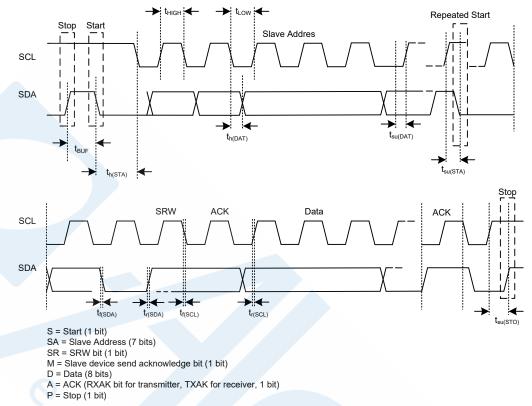

# I<sup>2</sup>C Characteristics

Ta=-40°C~85°C, unless otherwise specified

| Symbol               | Parameter                                      | Test Conditions | Min. | Тур.     | Max. | Unit |

|----------------------|------------------------------------------------|-----------------|------|----------|------|------|

| f <sub>SCL</sub>     | Serial Clock Frequency                         | _               | _    | _        | 1    | MHz  |

| t <sub>BUF</sub>     | Bus Free Time between Stop and Start Condition | SCL=1MHz        | 250  | _        | _    | ns   |

| t <sub>LOW</sub>     | SCL Low Time                                   | SCL=1MHz        | 500  | _        | _    | ns   |

| t <sub>HIGH</sub>    | SCL High Time                                  | SCL=1MHz        | 500  | _        | _    | ns   |

| t <sub>su(DAT)</sub> | Data Setup Time                                | SCL=1MHz        | 100  | <b>I</b> | _    | ns   |

| t <sub>su(STA)</sub> | Start Condition Setup Time                     | SCL=1MHz        | 250  | -        | _    | ns   |

| t <sub>su(STO)</sub> | Stop Condition Setup Time                      | SCL=1MHz        | 250  | -        | _    | ns   |

| t <sub>h(DAT)</sub>  | Data Hold Time                                 | SCL=1MHz        | 100  | <b>/</b> |      | ns   |

| t <sub>h(STA)</sub>  | Start Condition Hold Time                      | SCL=1MHz        | 250  | _        | _    | ns   |

| t <sub>r(SCL)</sub>  | Rise Time of SCL Signal                        | SCL=1MHz        | _    | _        | 100  | ns   |

| t <sub>f(SCL)</sub>  | Fall Time of SCL Signal                        | SCL=1MHz        | _    | _        | 100  | ns   |

| t <sub>r(SDA)</sub>  | Rise Time of SDA Signal                        | SCL=1MHz        | /—   | _        | 100  | ns   |

| t <sub>f(SDA)</sub>  | Fall Time of SDA Signal                        | SCL=1MHz        | _    | _        | 100  | ns   |

Rev. 1.00 4 January 12, 2022

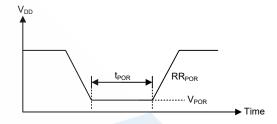

#### **Power on Reset Characteristics**

Ta=25°C

| Symbol            | Parameter                                                                           | Conditions | Min.  | Тур. | Max. | Unit |

|-------------------|-------------------------------------------------------------------------------------|------------|-------|------|------|------|

| V <sub>POR</sub>  | V <sub>DD</sub> Start Voltage to Ensure Power-on Reset                              | _          | _     | _    | 100  | mV   |

| RR <sub>POR</sub> | V <sub>DD</sub> Rising Rate to Ensure Power-on Reset                                | _          | 0.035 | _    | _    | V/ms |

| t <sub>POR</sub>  | Minimum Time for V <sub>DD</sub> Stays at V <sub>POR</sub> to Ensure Power-on Reset | _          | 1     | _    | _    | ms   |

## **Functional Description**

The BC2502x devices are ultra-low power, high performance, low-cost FSK receivers suitable for use in wireless applications with a frequency of 315, 433, 868, 915MHz respectively. The devices are formed by a low-IF receiver, followed by a FSK demodulator and a fractional-N synthesizer. They only require a crystal and a minimum number of passive components to implement a FSK receiver.

#### **FSK RF Receiver**

The BC2502x devices adopt a fully-integrated, low-IF receiver architecture. The received RF signal is first amplified by a low noise amplifier (LNA), after which the frequency is reduced to an intermediate frequency (IF). The IF signal is filtered by a channel-selected filter which rejects the unwanted out-of-band interference signals and image signal. After the BPF stage, the desired IF signal is amplified by the limiter amplifier which generates a received-signal-strength-indicator (RSSI) signal.

The devices feature an automatic gain control (AGC) unit which adjusts the front-end gain according to the RSSI. The AGC can increase the dynamic range of the RSSI and enable the devices to receive a wide dynamic range RF signal.

The FSK one/zero type data is generated by comparing the RSSI signal to a manipulated threshold. This threshold is crucial to the performance of FSK demodulation. The agile threshold detection mechanism can reduce glitches when there is no RF signal or when long zero data streams are received. It also includes a fast tracking threshold to offer good immunity from co-channel interferences.

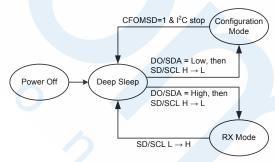

### **Operation Modes**

The devices provide four operation modes, power off mode, deep sleep mode, RX mode and configuration mode.

In the deep sleep mode, there is less than  $1\mu A$  of sleep mode leakage current with register data retention.

In the RX Mode, the devices execute normal RX operations that receive incoming RF signals from the antenna and then output the demodulated data onto the DO/SDA pin.

In the Configuration Mode, the devices are operated as  $I^2C$  slaves and are programmed by an external MCU. Users can select the desired RX channel by configuring the internal registers. After the configuration has completed, the devices will return to the deep sleep mode by setting the CFOMSD bit high.

**Operation Mode Switching**

Note: The CFOMSD bit will be cleared to zero automatically when the device leaves the configuration mode.

Rev. 1.00 5 January 12, 2022

#### **Sniff RX Mode**

The devices also provide a Sniff RX mode as it is controlled by an MCU. The SD/SCL pin defaults to a pull-high state. After power-on the devices will enter the deep sleep mode. An MCU could control the SD/SCL pin to make it enter or leave the RX mode. With additional SD/SCL control, users can optimize the average power consumption based on their applications.

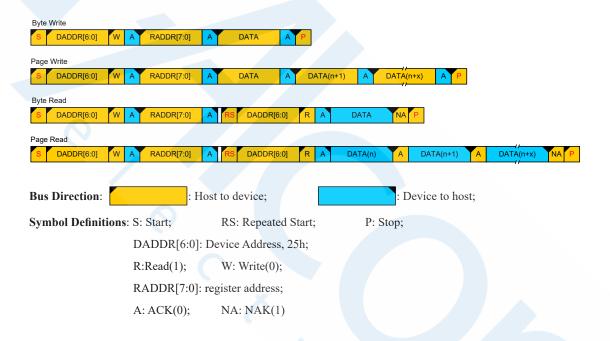

## **Configuration Mode**

The devices include an I<sup>2</sup>C serial interface, which is used for bidirectional, two-line communication between multiple I<sup>2</sup>C devices. The two lines of this interface are the serial data line, SDA, and the serial clock line, SCL. Both lines are equipped with

de-bounce functions. After a power on reset, these two pins are pulled to DVDD by default using internal pull-high resistors. When entering the RX mode, the pull-high resistors are disconnected.

The devices support the I<sup>2</sup>C format for byte write, page write, byte read and page read formats. Every byte placed onto the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit, MSB, first.

It should be noted that the I<sup>2</sup>C is a non-standard I<sup>2</sup>C interface, which only supports a single device for connection.

Rev. 1.00 6 January 12, 2022

I<sup>2</sup>C Communication Timing Diagram

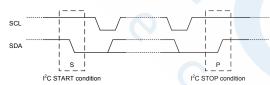

#### I<sup>2</sup>C START and STOP Conditions

- A high to low transition on the SDA line while SCL is high defines a START condition.

- A low to high transition on the SDA line while SCL is high defines a STOP condition.

- START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

• The bus remains busy if a Repeated START (RS) is generated instead of a STOP condition. The START (S) and Repeated START (RS) conditions are functionally identical.

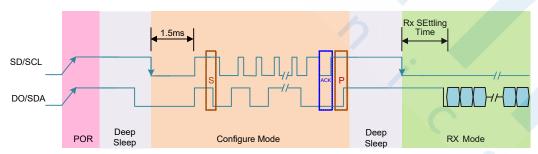

#### **Configuration Mode Switching and Timing**

As shown in the following diagram, when SDA is low and a SCL falling edge occurs, the device changes from the Deep Sleep Mode to the Configuration Mode after a 1.5ms delay time. If the SCL level remains high for a time greater than or equal to 20ms, the device will be forced to leave the Configuration Mode.

If the devices are connected to an MCU through an I<sup>2</sup>C interface, users can set the CFOMSD bit of the register, at address 40h, to leave the Configuration Mode.

**Entering and Leaving Configuration Mode Timing Diagram**

Rev. 1.00 7 January 12, 2022

# **Register Map**

When connected to an external MCU, the device's RF frequency can be setup using a series of internal registers in the Configuration Mode. The register data is written to and read from the devices using their internal I<sup>2</sup>C interface. The following provides a summary of all internal registers and their detailed descriptions.

| Addusss | Register |   |          |          | В     | Bit      |      |        |           |

|---------|----------|---|----------|----------|-------|----------|------|--------|-----------|

| Address | Name     | 7 | 6        | 5        | 4     | 2        | 1    | 0      |           |

| 00h     | _        |   |          |          | Rese  | erved    |      |        |           |

| 05h     | FSKDM1   |   |          | Res      | erved |          |      | MDIV_S | SEL [1:0] |

| 06h     | _        |   |          |          | Rese  | erved    |      |        |           |

| 07h     | -        |   |          |          | Rese  | erved    |      |        |           |

| 09h     | -/       |   |          |          | Rese  | erved    |      |        |           |

| 0Ah     | _        |   |          |          | Rese  | erved    |      |        |           |

| 10h     | OM       | _ | BAND_S   | SEL[1:0] | _     | _        | _    | _      | _         |

| 11h     | _        |   |          |          | Rese  | erved    |      |        |           |

| 12h     | SX1      | _ |          |          |       | D_N[6:0] |      |        |           |

| 13h     | SX2      |   |          |          | D_K   | [7:0]    |      |        |           |

| 14h     | SX3      |   |          |          | D_K   | [15:8]   |      |        |           |

| 15h     | SX4      |   | _        | -        |       |          | D_K[ | 19:16] |           |

| 1Bh     | _        |   |          |          | Rese  | erved    |      |        |           |

| 1Fh     |          |   | Reserved |          |       |          |      |        |           |

| 32h     | _        |   | Reserved |          |       |          |      |        |           |

| 40h     | I2C1     |   | Reserved |          |       |          |      |        |           |

| 46h     | _        |   |          |          | Rese  | erved    |      |        |           |

Note: The addresses which are not listed in this table are reserved for future use, it is suggested not to change their initial values by any methods.

The recommended values for the registers are listed below:

| Addr. | Setting | Addr. | Setting |

|-------|---------|-------|---------|

| 00h   | 60h     | 11h   | 69h     |

| 06h   | 71h     | 1Bh   | 2Fh     |

| 07h   | 07h     | 1Fh   | 10h     |

| 09h   | 7Fh     | 32h   | 82h     |

| 0Ah   | 7Fh     | 46h   | 01h     |

#### • FSKDM1 - FSK De-Modulator Control Register 1 (Addr: 05H)

| Bit  | 7 | 6 | 5 | 4   | 3          | 2 | 1      | 0         |

|------|---|---|---|-----|------------|---|--------|-----------|

| Name | _ | _ | _ | _   | _          | _ | MDIV_S | SEL [1:0] |

| R/W  | _ | _ | _ | - / | <b>7</b> – | _ | R/     | W W       |

| POR  | 1 | 0 | 0 | 0   | 0          | 0 | 0      | 1         |

Bit 7~2 Reserved bit, cannot be changed

Bit 1~0 MDIV\_SEL[1:0]: Demodulator operation clock divider selection

00: 187.2kHz 01: 936.kHz 10: 46.8kHz 11: reserved

Rev. 1.00 8 January 12, 2022

#### • OM - Operation Mode Control Register (Addr: 10H)

| Bit  | 7 | 6      | 5             | 4 | 3 | 2 | 1 | 0 |

|------|---|--------|---------------|---|---|---|---|---|

| Name | _ | BAND_S | BAND_SEL[1:0] |   | _ | _ | _ | _ |

| R/W  | _ | R/     | W             | _ | _ | _ | _ | _ |

| POR  | 0 | 0      | 0             | 0 | 0 | 0 | 0 | 0 |

Bit 7 Reserved bit, cannot be changed

Bit 6~5 BAND\_SEL[1:0]: Band selection

00: 300~360MHz Band 01: 390~450MHz Band

10: Reserved

11: 850~935MHz Band (BC2502B Only)

Bit 4~0 Reserved bit, cannot be changed

#### • SX1 - Fractional-N Synthesizer Control Register 1 (Addr: 12H)

| Bit  | 7 | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

|------|---|---|---|---|----------|---|---|---|

| Name | _ |   |   |   | D_N[6:0] |   |   |   |

| R/W  | _ |   |   |   | R/W      |   |   |   |

| POR  | 0 | 0 | 1 | 0 | 1        | 0 | 1 | 1 |

Bit 7 Reserved bit, cannot be changed

Bit 6~0 **D\_N[6:0]**: RF channel frequency integer number code

D\_N[6:0]=Floor (

$$\frac{f_{RF}-f_{IF}}{f_{XTAL}\div2}\times0.8)\times M,$$

(315MHz: M=2, Other Bands: M=1)

For example:

f<sub>XTAL</sub>=16MHz, RF channel frequency(f<sub>RF</sub>)=315MHz, Intermediate Frequency (f<sub>IF</sub>)=200kHz

- $\rightarrow$  (315MHz-0.2MHz)/(16MHz/2)×0.8×2=62.96

- $\rightarrow$  D N=62

- $\rightarrow$  Dec2Bin(62)=011\_1110

f<sub>XTAL</sub>=16MHz, RF channel frequency(f<sub>RF</sub>)=433.92MHz, Intermediate Frequency (f<sub>IF</sub>)=200kHz

- $\rightarrow$  (433.92MHz-0.2MHz)/(16MHz/2)×0.8=43.372

- $\rightarrow$  D N=43

- $\rightarrow$  Dec2Bin(43)=010 1011

#### • SX2 - Fractional-N Synthesizer Control Register 2 (Addr: 13H)

| Bit  | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|----------|---|---|---|---|---|---|---|

| Name | D_K[7:0] |   |   |   |   |   |   |   |

| R/W  | R/W      |   |   |   |   |   |   |   |

| POR  | 1        | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

Bit 7~0 **D\_K[7:0]**: RF channel frequency fractional number code lowest byte

## • SX3 – Fractional-N Synthesizer Control Register 3 (Addr: 14H)

| Bit  | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|-----------|---|---|---|---|---|---|---|

| Name | D_K[15:8] |   |   |   |   |   |   |   |

| R/W  | R/W       |   |   |   |   |   |   |   |

| POR  | 1         | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

Bit 7~0 D\_K[15:8]: RF channel frequency fractional number code medium byte

Rev. 1.00 9 January 12, 2022

#### • SX4 - Fractional-N Synthesizer Control Register 4 (Addr: 15H)

| Bit  | 7 | 6 | 5 | 4 | 3          | 2 | 1 | 0 |

|------|---|---|---|---|------------|---|---|---|

| Name | _ | _ | _ | _ | D_K[19:16] |   |   |   |

| R/W  | _ | _ | _ | _ | R/W        |   |   |   |

| POR  | 0 | 1 | 1 | 0 | 0          | 1 | 0 | 1 |

Bit 7~4 Reserved bit, cannot be changed

Bit 3~0 **D\_K[19:16]**: RF channel frequency fractional number code highest byte

$$D_{-}K[19:0] = Floor \ \{(\frac{f_{RF} - f_{IF}}{f_{XTAL} \div 2} \times 0.8 \times M - D_{-}N[6:0] \times 2^{20}\}, \ (315MHz: M=2, Other \ Bands: M=1)\}$$

For example:

f<sub>XTAL</sub>=16MHz, RF channel frequency(f<sub>RF</sub>)=315MHz, Intermediate Frequency (f<sub>IF</sub>)=200kHz

- $\rightarrow$  (315MHz-0.2MHz)/(16MHz/2)×0.8×2=62.96

- $\rightarrow$  D K=0.96×2<sup>20</sup>=1006632

- → Dec2Bin(1006632)=1111\_0101\_1100\_0010\_1000

f<sub>XTAL</sub>=16MHz, RF channel frequency(f<sub>RF</sub>)=433.92MHz, Intermediate Frequency (f<sub>IF</sub>)=200kHz

- $\rightarrow$  (433.92MHz-0.2MHz)/(16MHz/2)×0.8=43.372

- $\rightarrow$  D K=0.372×2<sup>20</sup>=390070

- → Dec2Bin(390070)=0101\_1111\_0011\_1011\_0110

#### • I2C1 - I2C Control Register 1 (Addr: 40H)

| Bit  | 7 | 6 | 5            | 4 | 3 | 2 | 1 | 0      |

|------|---|---|--------------|---|---|---|---|--------|

| Name | _ | _ | <del>_</del> | _ | _ | _ | _ | CFOMSD |

| R/W  | _ | _ | _            | _ | _ | _ | _ | R/W    |

| POR  | 0 | 0 | 0            | 0 | 0 | 0 | 0 | 0      |

Bit 7~1 Reserved bit, cannot be changed

Bit 0 **CFOMSD**: Configuration Mode shut down control

0: No operation

1: Exit Configuration Mode

In the configuration mode the devices can be forced to leave this mode by first setting the CFOMSD bit high and then followed by an I<sup>2</sup>C stop condition. After leaving the Configuration Mode the CFOMSD bit will be reset to zero automatically.

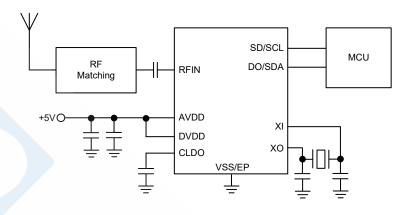

# **Application Circuits**

# **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- Packing Meterials Information

- Carton information

Rev. 1.00 12 January 12, 2022

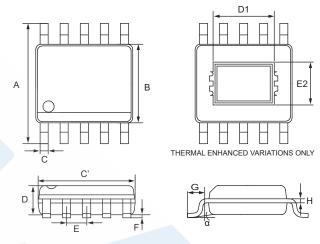

# 10-pin SOP-EP (150mil) Outline Dimensions

| Cumbal | Dimensions in inch |           |       |  |  |  |  |

|--------|--------------------|-----------|-------|--|--|--|--|

| Symbol | Min.               | Nom.      | Max.  |  |  |  |  |

| A      | _                  | 0.236 BSC | _     |  |  |  |  |

| В      | _                  | 0.154 BSC | _     |  |  |  |  |

| С      | 0.012              | _         | 0.018 |  |  |  |  |

| C'     | _                  | 0.193 BSC | _     |  |  |  |  |

| D      | <del>-</del>       | _         | 0.069 |  |  |  |  |

| D1     | 0.059              | _         | _     |  |  |  |  |

| E      |                    | 0.039 BSC | _     |  |  |  |  |

| E2     | 0.039              | _         | _     |  |  |  |  |

| F      | 0.000              | _         | 0.006 |  |  |  |  |

| G      | 0.016              | _         | 0.050 |  |  |  |  |

| Н      | 0.004              | _         | 0.010 |  |  |  |  |

| α 0°   |                    | _         | 8°    |  |  |  |  |

| Cumbal | Dimensions in mm |         |      |  |  |  |

|--------|------------------|---------|------|--|--|--|

| Symbol | Min.             | Nom.    | Max. |  |  |  |

| A      | -(               | 6.0 BSC |      |  |  |  |

| В      | _                | 3.9 BSC | _    |  |  |  |

| С      | 0.30             | _       | 0.45 |  |  |  |

| C'     | _                | 4.9 BSC | _    |  |  |  |

| D      | _                |         | 1.75 |  |  |  |

| D1     | 1.50             | 0 -     | _    |  |  |  |

| E      | _                | 1.0 BSC | _    |  |  |  |

| E2     | 1.00             |         | _    |  |  |  |

| F      | 0.00             |         | 0.15 |  |  |  |

| G      | 0.40             | _       | 1.27 |  |  |  |

| Н      | 0.10             |         | 0.25 |  |  |  |

| α      | 0°               | _       | 8°   |  |  |  |

Rev. 1.00 13 January 12, 2022

Singel 3 | B-2550 Kontich | Belgium | Tel. +32 (0)3 458 30 33 info@alcom.be | www.alcom.be Rivium 1e straat 52 | 2909 LE Capelle aan den IJssel | The Netherlands Tel. +31 (0)10 288 25 00 | info@alcom.nl | www.alcom.nl

## Copyright<sup>©</sup> 2022 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.

Rev. 1.00 14 January 12, 2022